## THE STABILIZATION SYSTEM OF 400-750 KV PULSED ACCELERATING VOLTAGE

V.N.Zubetz, V.I.Derbilov, S.K.Esin, E.S.Nikulin, O.T.Frolov, V.P.Yakushev Institute for Nuclear Research, RAS, Moscow

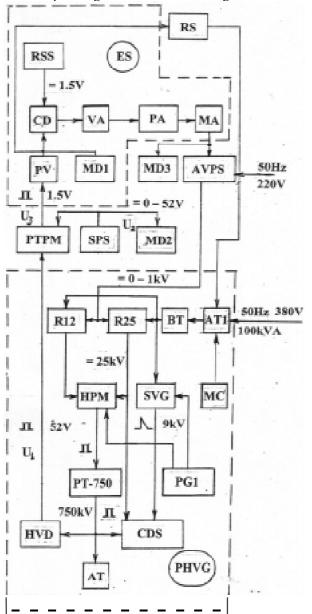

The stabilization system of both pulsed accelerating voltage with amplitudes up to 750 kV and duration up to 85 mcsec, and 400 kV pulses with 150 mcsec duration runs at the proton injector of the linac of the Moscow meson factory [1] and provides stability of voltage during 750 kV pulse not worse than  $\pm 0,1$ %, and from pulse to pulse not worse than  $\pm 0,04$ %. The structural scheme of the pulse high-voltage stable amplitude generator is shown in Fig. 1.

Fig. 1. The structural scheme of the pulse high-voltage stable amplitude generator.

The stabilization represents a compensatory stabilizer with an adjusting element connected in sequence. The latter is the «additional voltage» power source (AVPS) which develops a constant voltage from

0 up to 0.8kV, connected in sequence to 12kV and 25kV voltage sources. 12kV (R12) and 25kV (R25) rectifiers are fed from the 50Hz three-phase network through the adjustable transformer (AT1) and step-up transformer (BT). AVPS, R12 and R25 feed the high-voltage pulse modulator (HPM). The output signal of the modulator is supplied with amplitude up to 16kV to a primary winding of pulse transformer (PT-750), the secondary winding of which is loaded with currents: capacity-diode stabilizer (CDS) [2]; beam of the accelerating tube (AT); AT water divider. The main load for PT-750 is CDS; it suppresses oscillations originating in PT-750 during the formation of 750kV high-voltage impulse, and also determines pulse amplitude, which is proportional to R25 voltage.

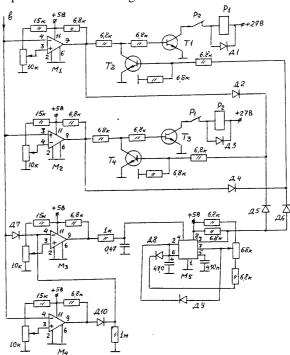

Fig. 2. The relay stabilizer scheme.

For measuring the high-voltage pulse amplitude the capacity-type high-voltage divider (HVD) is used. U1 feedback signal from HVD with amplitude about 52V is applied at the input of the pulse top precision meter (PTPM) and is compared with U2 constant voltage developed by stabilized power source (SPS). As a result we have a mismatching signal U3=U1-U2 with the level of about 1.5V representing the cut of the upper part of the U1 feedback signal. To control the U2 voltage the measuring device MD2 is used. The U3 pulse signal of mismatching is applied to the input of the electronic stabilizer (ES), where it will be converted by a peak voltmeter (PV) into the constant positive voltage with the value proportional to the U3 amplitude and monitored by measuring device MD1. The signal from PV is applied to the input of the comparator device (CD); negative 1.5V voltage from the reference supply source (RSS) is applied to the other CD input.

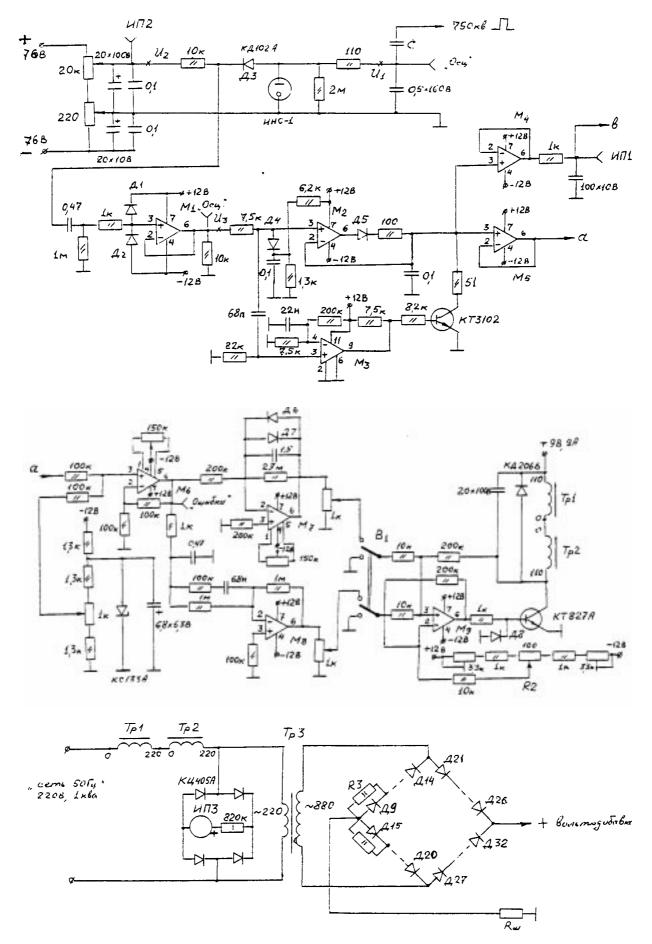

Fig. 3. The high-voltage pulse stabilizer scheme.

The difference signal is amplified: by the voltage amplifier (VA); by the power amplifier (PA); by the magnetic amplifier (MA). The MA load is AVPS. To control MA output voltage the MD3 measuring device is used. As U1 voltage is increased the U3 value is also raises; this results in decrease of the «additional voltage» and therefore in decrease of U1, and vise versa. The transition to the new U1 stabilized value is realized by U2 variation, and by AT1 regulation in case the system has exceeded the bounds of the zone of electronic stabilizing. AT1 regulation may be realized both "manually"- through the manual control (MC), and automatically - through the relay stabilizer (RS). The 2V-variation of UIPM reference voltage corresponds to the greatest (200V) possible variation of MA output signal - the whole range of electronic stabilizing. When there are greater mismatches in the stabilization system, RS performs a continuous AT1 output voltage variation in the direction of reducing mismatch. When approaching a zone of electronic stabilizing, RS performs a pulsed AT1 voltage variation. The last RS impulse sets AT1 voltage level approximately at the center of the zone of electronic stabilizing. That is how a smooth transition from the relay mode of stabilizing to the electronic one is achieved.

The RS electric scheme is shown in Fig.2. PV output signal serves as a driving signal for RS. C1 and C2 comparators exercise a continuous control over AT1; C3 and C4 comparators and the generator based on C5 chip exercises pulse modulation of AT1 continuous control.

As a result, PHVG instability from pulse to pulse is now not worse than  $\pm 0.04\%$ .

The scheme of the stabilizer of high-voltage pulses is shown in Fig. 3. PTPM is realized on M1 chip, C1 capacitor and D3 diode. PV is based on M2 chip, D5 diode, C2 capacitor. M3 chip and T1 transistor produce approximately 50% PV «step reduction» in the beginning of each pulse. M4 and M5 chips serve for the matching of PV output with MD1 and CD input. CD is the voltage repeater based on M6 chip. Two signals are applied to its non-inverting input: a positive signal from PV and a negative signal from RSS. The difference signal is applied to VA, which consists of the integrator based on M7 chip and differentiator based on M8 chip. The basic elements of PA are: M9 chip and T2 output transistor loaded with MA which includes transformers Tr1 and Tr2. AVPS includes the step-up transformer Tr3 and the rectifying bridge.

The top of high-voltage pulse is controlled by CDS, but due to current flow in CDS during pulse the voltage increases sawtoothly by approximately 9kV. The sawtoothly reducing voltage generator (SVG) with the amplitude 9kVand duration 150mcsec was made in 1995. SVG has a manual amplitude adjustment and a delayed-pulse generator triggering (PG1).

The sawtooth voltage is formed at grounding resistor 0.3kOm which is connected with the low-voltage CDS terminal when the capacitor C=36mcF discharges through a thyristor and a pulse step-up transformer. This facility allows to compensate the irregularity of the amplitude on the top of high-voltage pulse up to the level as low as  $\pm 0.1$  %.

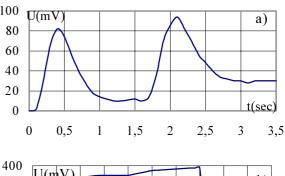

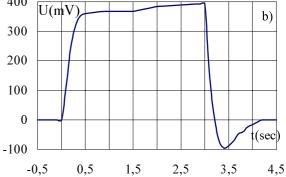

Time responses of the closed stabilization system loop are shown in Fig.4 where the variations of CD output mismatch signal are indicated at: a) two-step network voltage variation; b) feedback loop disclosing and closing. The transition period is 1.1s.

Fig.4. Time responses of mismatch signal variation

## REFERENCES

- 1. A.S.Belov et al. Proceedings of the XII International Conference on Electrostatic Accelerators. Obninsk (in Russian), 1997, p.199.

- V.N.Zubetz et al. Operation of the 400-750kV Pulse Voltage Multi-cascade Discriminator. // Problems of Atomic Science and Techn. 1999. v. 3. Issue: Nuclear Physics Researches. (35), p. 38.

- A.V.Fateev. Raschet avtomaticheskih sistem. Moskva, Visshaya shkola, (in Russian) 1973, p. 205-211.